公式ドキュメントは、以下のサイトからダウンロードできます。

Epiphanyアーキテクチャー・リファレンス・マニュアル、SDK リファレンス・マニュアル、データ・シート等

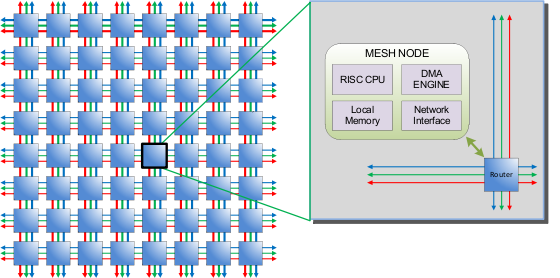

Epiphanyアーキテクチャーは、以下の要素から構成されます。

Epiphanyアーキテクチャーは幅広いアプリケーションにおいて良好な性能を発揮するように設計されていますが、特にコードやデータが空間的・時間的にローカリティーのあるアプリケーションにおいて卓越した性能を示します。そのようなアプリケーションの例としては、画像処理、通信、センサー信号処理、暗号処理などがあります。

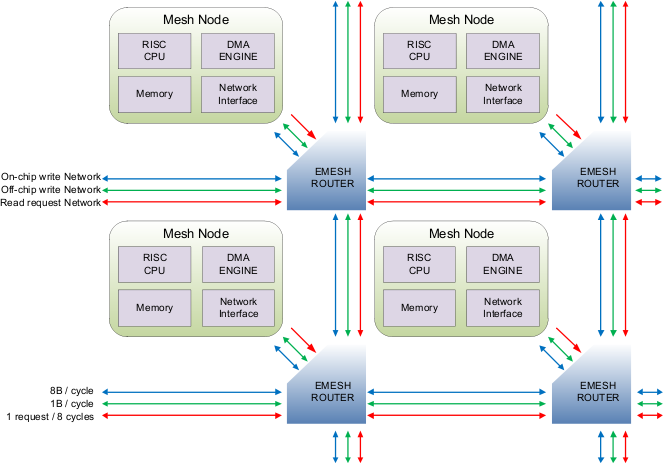

各ノード間の高速通信はEpiphanyアーキテクチャーの2D eMesh Network-On-Chip(NoC)によって実現されます。メッシュ・メットワークは高スループットのリアルタイム・アプリケーションにおけるトラフィック・パターンを効果的に扱えます。多くのデータを1サイクルで通信するためには各ノード間に多数の配線が必要ですが、メッシュ型のネットワークはそれを省スペースで実現できるという利点があります。

各ルーティング・リンクは8 Bytes/cycleの転送能力を持ち、各ルーティング・ノードにおいて64 Bytes/cycleの転送が可能となっています。動作クロックが1 GHzの場合、64 GB/secの帯域幅をサポートします。

Epiphanyアーキテクチャーのメモリー・マップはフラットかつ非保護となっています。各メッシュ・ノードは無制限にメモリー・システムの全域に直接アクセス可能です。Epiphanyアーキテクチャーはフラットな32 bitアドレスのメモリー・マップと4096までの独立したメッシュ・ノードをサポートしています。

共有メモリー・アーキテクチャーと低遅延のオン・チップ・メッシュ・ネットワークは、非常に小さなオーバーヘッドで数バイトから数キロバイトに渡るメッセージの受け渡しを可能にしています。

eMesh NoCの広い帯域と少ない遅延は、細粒度のタスクの並列実行から大きなカーネルの実行までを可能にします。Epiphanyアーキテクチャーは様々なレベルの並列性に対応しているため、並列プログラミングがより簡単になり、タスク間通信のボトルネックを大幅に削減します。

Epiphanyアーキテクチャーの特長:

具体的には、以下の表のように順序付けされます。

| 最初の命令 | 次の命令 | 順序付けされるか |

|---|---|---|

| コアXからの読み込み | コアXからの読み込み | ○ |

| コアXへの書き込み | コアXへの書き込み | ○ |

| コアXへの書き込み | コアXからの読み込み | × |

| コアXからの読み込み | コアXへの書き込み | ○ |

| コアXからの読み込み | コアYからの読み込み | ○ |

| コアXへの書き込み | コアYへの書き込み | × |

| コアXへの書き込み | コアYからの読み込み | × |

| コアXからの読み込み | コアYへの書き込み | ○ |

Epiphanyアーキテクチャーのメモリー・アーキテクチャーは、リトル・エンディアンです。

全てのデータの格納アドレスは、そのデータ・サイズに合わせて「整列」されていなければなりません。整列されていないデータへのアクセスは、例外を発生します。非整列のストアでは、間違った値がメモリーに書き込まれます。非整列のロードでは、例外が発生する前に間違った値がレジスターに読み込まれます。各データ・タイプにおける格納アドレスの下位ビットは、以下のようになっていなければなりません。(「x」は1または0の値をとります。)

| データ・タイプ | アドレスの下位3ビット |

|---|---|

| バイト | xxx |

| ハーフ・ワード(2バイト) | xx0 |

| ワード(4バイト) | x00 |

| ダブル・ワード(8バイト) | 000 |

全ての命令は、ハーフ・ワード(2バイト)境界に整列されていなければなりません。

各コアには32bit x 64個のレジスターがあります。そのうち45個が汎用レジスターとして使用できます。64bitの値のロード・ストアも可能です。

全ての命令は16bit長バージョンと32bit長バージョンがあります。16bit長バージョンを利用すれば、コードサイズや消費電力を減らすことができます。ただし、16bit長バージョンでは利用できるレジスターや即値のサイズに制限があります。

ロード命令やストア命令では、ローカル・メモリーだけでなく他のコアのメモリーや外部メモリーにアクセスできます。(ただし、効率を考慮すればローカル・メモリー以外へのアクセスにはDMAを積極的に利用すべきです。)

ロード・ストアのアドレッシング・モードには以下の種類があります。

条件付きムーブ命令があるので、単純な条件分岐は分岐ミスのペナルティの影響を受けることなく実行することができます。

Epiphany eCore CPUには動的分岐予測機構はありません。分岐は、常に「分岐しない」方向に静的に予測されます。条件分岐で分岐しない場合のペナルティは0サイクルです。

分岐した場合は、必ず3サイクルの分岐ミス・ペナルティが発生します。一般的なCPUの分岐ミス・ペナルティに比べれば僅かなものですが、極めて小さなループ等では、ロスを最小化するために、ループ・アンロール等のテクニックが有効です。

Epiphanyの各プロセッサ・ノードは、独立したDMAエンジンを備えています。

DMAエンジンはCPUと同じクロックで動作し、1クロックあたり64ビットのデータを転送します。クロック1GHzの構成において最大8ギガバイト毎秒の連続転送が可能です。

このDMAエンジンには以下の特徴があります。

【表】DMA転送の種類

| ソース | デスティネーション | 機能 |

|---|---|---|

| ローカルメモリー | 外部メモリー | 4つのローカル・メモリー・バンクのうちの一つからデータを読み出し、eMeshネットワークに書き込み処理として送信します。 |

| 外部メモリー | ローカルメモリー | eMeshネットワークに読み込みリクエストを出します。ブロッキング(データ転送が完了するまで停止)、もしくはノンブロッキング(転送を待たずに即座に戻る)処理を選択できます。 |

| オートDMAレジスター | ローカルメモリー | 外部マスタから書き込ませます。これはスレーブ・モードに設定されている場合に使用されます。 |

| 外部メモリー | 外部メモリー | eMeshネットワークに読み込みトランザクションを送信します。読み込みトランザクションはスプリット・トランザクションなのでデスティネーションは任意に設定可能です。書き込み先のメモリーはスプリット・トランザクション・ルーティング・モードをサポートしている必要があります。 |

DMAエンジンは2つの独立したチャンネルを持ち、それぞれマスター・モードもしくはスレーブ・モードとして動作可能です。

スレーブ・モードでは転送のペースは外部のマスターによって制御されます。マスター・モードではメモリーとインターフェースのリソースが許す限り毎クロック、トランザクションを発行します。

DMAディスクリプターは以下のように構成されます。全てのディスクリプターはローカル・メモリーに置かれ、ダブル・ワード境界にアラインされている必要があります。

ディスクリプターはスタートアップ・ビットに1がセットされた場合、もしくはチェイニング・モードに設定された場合にDMAチャンネル・コンフィギュレーション・レジスター・セットに読み込まれます。チェイニング・モードでは転送が完了すると自動的に次のディスクリプターが読み込まれます。

| Addr0+7, Addr0+6 | Addr0+5, Addr0+4 | Addr0+3, Addr0+2 | Addr0+1, Addr0 |

|---|---|---|---|

| STRIDE-INNER-DST | STRIDE-INNER-SRC | NXT_PTR | DMACONFIG |

| STRIDE-OUTER-DST | STRIDE-OUTER-SRC | CNT-OUTER | CNT-INNER |

| DST ADDRESS(HI) | DST ADDRESS(LO) | SRC ADDRESS(HI) | SRC ADDRESS(LO) |

DMAチャンネルの優先度は固定となっており、チャンネル0は常にチャンネル1よりも高い優先度で実行されます。

DMAはミス・アラインド・アクセスや存在しないアドレスへのアクセスに対してエラーを報告しません。このようなシナリオでは、予期しない動作がおこり、コアやチップはリセットが必要な状態になるかも知れません。