Icarus Verilogコンパイラを使う

Icarus Verilogは、オープンソースのVerilogコンパイラ&シミュレータです。通常のPC上でVerilogソースコードのコンパイルとシミュレーションを行うことができます。

手軽にインストールでき、FPGAベンダのツールよりも軽く、動作が速いのでVerilog HDLの学習に適しています。

今回はこれをUbuntuにインストールして使ってみます。

PCにUbuntuをインストールする方法については、「Parallella Fan!:PCにUbuntu 14.04 (Trusty Tahr)を「軽量化」インストールする」を参照してください。

Icarus Verilogとgtkwaveをインストール

gtkwaveは波形ビューワです。Icarus Verilogが出力した波形データを視覚化して表示することができます。これもいっしょにインストールします。

端末で、

sudo apt-get install iverilog gtkwave

基本的な使い方

コンパイル方法:

iverilog -o 出力実行ファイル名 Verilogソースコードファイル名

シミュレーション方法:

vvp 実行ファイル名

サンプルソースコードのダウンロード、コンパイル、実行

簡単なサンプルを作りました。レジスタをカウントアップする回路です。

mkdir -p ~/icarus_files

cd ~/icarus_files

wget https://cellspe.matrix.jp/zerofpga/files/counter_v.tar.gz

tar xzf counter_v.tar.gz

cd counter_v

./run.sh

コンパイルとシミュレーションが行われ、「wave.vcd」という波形データファイルが生成されます。また、シミュレーション実行時にカウンターの値を表示するようにしています。

ソースコード

ハードウェア記述:counter.v

Copyright (c) 2014, miya

All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

module counter

(

// ポート宣言

// クロック

input CLK,

// リセット

input RESET,

// 32bit カウンター

output reg [31:0] COUNT

// 最後の項目にはカンマを付けてはいけない(文法エラー)

);

// このブロックはクロックの立ち上がり(positive edge:0→1)で毎回実行される

always @(posedge CLK)

begin

if (RESET == 1'b1)

// RESETが1ならカウンターをリセット

begin

COUNT <= 32'd0;

end

else

// 通常時はカウンターに1を足す

begin

COUNT <= COUNT + 32'd1;

end

end

endmodule

テストベンチ:counter_testbench.v

Copyright (c) 2014, miya

All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED.

IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

// 単位時間を1ナノ秒に設定

`timescale 1ns / 1ps

module counter_testbench;

// テストベンチのモジュールにはポートリストはない

parameter STEP = 10; // 10ナノ秒:100MHz

parameter TICKS = 19;

reg TEST_CLK;

reg TEST_RESET;

wire [31:0] TEST_COUNT;

// 各 initial ブロックは並列に実行される

// シミュレーション設定

initial

begin

// wave.vcd という名前で波形データファイルを出力

$dumpfile("wave.vcd");

// counter_1 に含まれる全てのポートを波形データに含める

$dumpvars(0, counter_1);

// シミュレータ実行時に counter_1 のポート COUNT を

// モニタする(値が変化した時に表示)

$monitor("COUNT: %d", counter_1.COUNT);

end

// クロックを生成

initial

begin

TEST_CLK = 1'b1;

forever

begin

// #数値 で指定時間遅延させる

// ~ でビット反転

#(STEP / 2) TEST_CLK = ~TEST_CLK;

end

end

// 同期リセット信号を生成

initial

begin

TEST_RESET = 1'b0;

// 2クロックの間リセット

repeat (2) @(posedge TEST_CLK) TEST_RESET <= 1'b1;

@(posedge TEST_CLK) TEST_RESET <= 1'b0;

end

// 指定クロックでシミュレーションを終了させる

initial

begin

repeat (TICKS) @(posedge TEST_CLK);

$finish;

end

// counter_1 という名前で counter モジュールをインスタンス化

counter counter_1

(

.CLK (TEST_CLK),

.RESET (TEST_RESET),

.COUNT (TEST_COUNT)

);

endmodule

コンパイル・実行スクリプト:run.sh

EXE=main

iverilog -o $EXE *.v

if [ $? -eq 0 ]; then

vvp $EXE

fi

gtkwaveの使用方法

gtkwaveを起動します。

アプリケーション・ランチャからGTKWaveを起動するか、端末で「gtkwave &」を実行します。

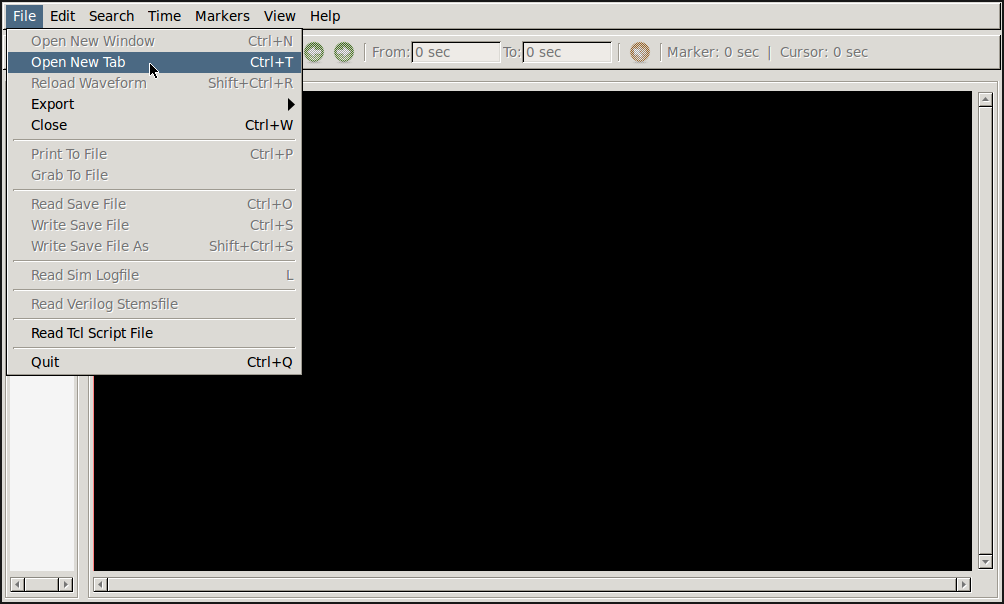

メニューからFile→Open New Tabを選択します。

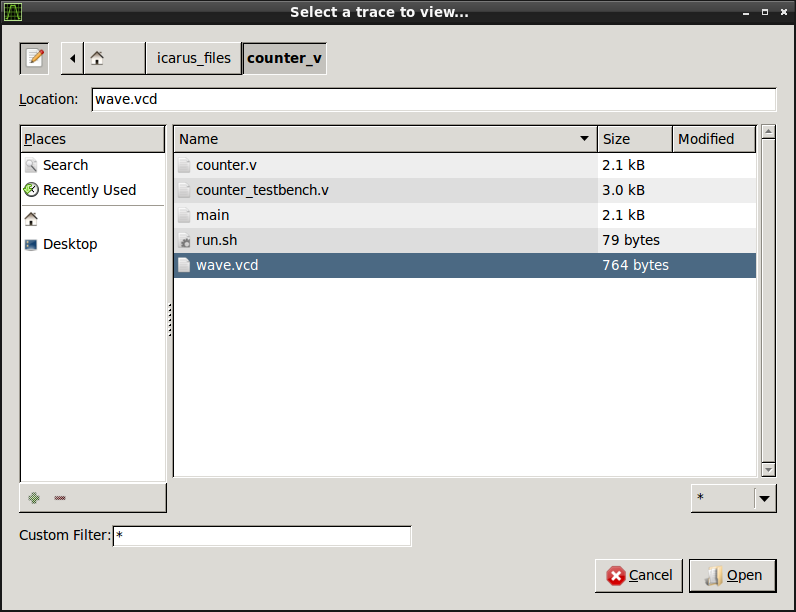

先ほどシミュレーターで生成したファイル、ホームディレクトリ/icarus_files/counter_v/wave.vcd を選択して「Open」をクリックします。

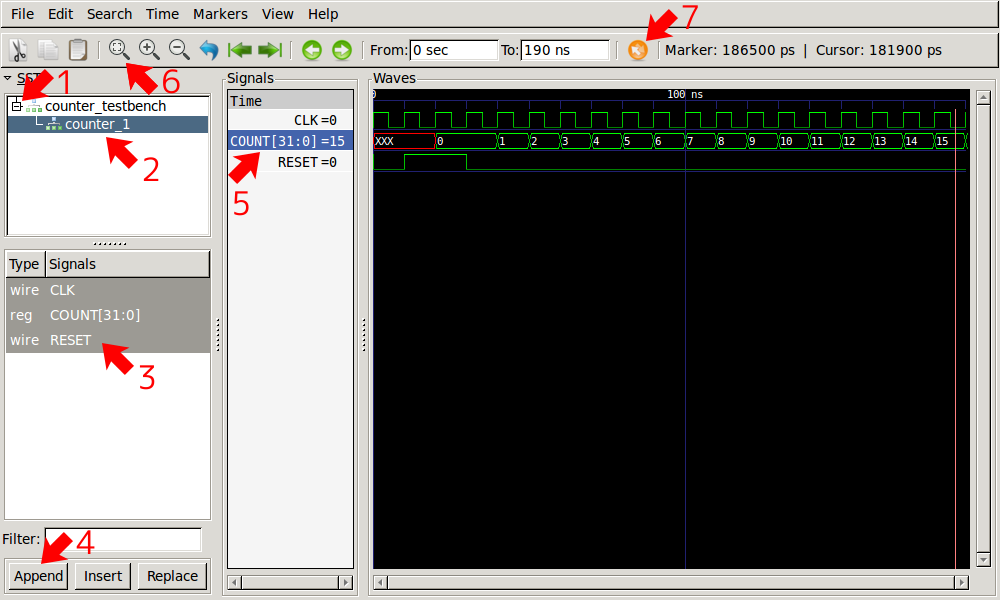

1. 「counter_testbench」の左側の「+」をクリックします。

2. 「counter_1」が出てくるのでそれをクリックします。

3. 信号名が表示されるので、3つの信号全部を選択します。一つ選んでからCtrl+A、もしくは、CtrlやShiftを押しながらマウスクリックで選んでいきます。

4. 「Append」をクリックします。

5. 「Signals」欄の「COUNT」を右クリックして、右クリックメニューからData Format→Decimalを選択します。これでそのベクタの値が十進表示されるようになります。

6. 「Zoom Fit」アイコンをクリックして拡大比率を画面にフィットさせます。

7. ソースコードを変更して再度コンパイル、シミュレートした場合、「Reload」ボタンをクリックして表示を更新します。

ここで調整した波形のレイアウトは、メニューからFile→Write Save File Asで保存することができます。「wave.gtkw」などのファイル名で保存しておいて、次回からはFile→Open New Tabでそのファイルをオープンすれば、保存したレイアウトですぐに表示できます。

このように、Icarus Verilogとgtkwaveを使用すれば、Verilogソースコードの変更、コンパイルとシミュレーション、シミュレーション結果を波形で確認、という作業を効率良く行うことができます。

参考文献

Icarus Verilog GitHub リポジトリ(外部リンク)

初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編(外部リンク)

初めてでも使えるVerilog HDL文法ガイド ―― 文法ガイド編(外部リンク)