オープンソースのEDAツール「Qflow」を使った半導体設計の方法

今回は番外編としてFPGAではなく、オープンソースのEDAツール「Qflow」でスタンダード・セル方式の半導体設計を行ってみました。QflowはHDLソースコードを元にスタンダード・セル(NAND等の論理素子をブロック化したもの)を用いて論理合成、配置配線を行い、最終的に半導体チップのレイアウトデータ(GDSIIファイル)を生成するツールです。

Qflowのインストール

Ubuntu等Debian系のLinux上で以下のコマンドでインストールします。

$ sudo apt-get install qflow qflow-tech-osu018 qflow-tech-osu035 qflow-tech-osu050 verilator gtkwave iverilog

ARM系アーキテクチャでも動作するのでKria KV260上のUbuntuやRaspberry Pi 5上のRaspberry Pi OS等でも使えます。ただし、Wayland環境とは相性が悪く、描画が異常に重くなってしまうので最近のWayland環境のRaspberry Pi OSではraspi-configでX環境に切り替えてください。

プロジェクト作成

QflowではFPGA向けに設計したVerilog HDLソースコードがほぼそのまま使えます。

まず、HDLのトップモジュールと同じ名前でプロジェクトディレクトリを作成します。(例えばmylogic.vというファイルにmodule mylogicを記述している場合、プロジェクトディレクトリ名もmylogicにします。)こうしておくとデフォルト設定で自動的にソースコードが読み込まれるので簡単です。

次に、その中に「source」というディレクトリを作り、その中にHDLのソースコードを入れます。

その他の設定ファイルなどは起動後に自動作成されるので、これだけでプロジェクトの準備は完了です。

Qflowの起動からGDSファイルの生成まで

ターミナルでプロジェクトディレクトリに移動します。

$ cd [プロジェクトディレクトリ]

QflowをGUIモードで起動します。

$ qflow gui

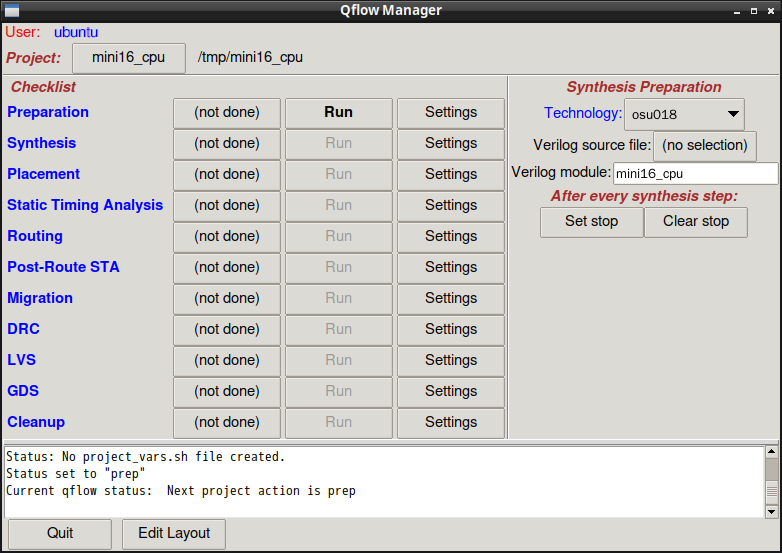

Qflow Managerが起動し、カレントディレクトリのプロジェクトが自動的に開かれます。基本的な操作方法は、各項目の「Settings」ボタンをクリックして設定、「Run」ボタンをクリックして実行です。デフォルトでは上から連続して実行されるようになっていますが、以下の順序で設定、実行することをおすすめします。

基本的な操作手順

ここに記載していない項目はデフォルトでOKです。

- Preparation: Settings

前記の方法でプロジェクトを作成している場合は「Preparation」の設定はデフォルトでOKです。「Technology:」からプロセスルールを選択します。(ここではosu018が180nmプロセスです)

- Preparation: Run

- Synthesis: Settings

Stop flow after synthesis: on

- Synthesis: Run

合成が実行されます。

- Placement: Settings

Initial density: 0.8

Aspect ratio: 0.75

Arrange Pins: Auto groupをクリック、次にApplyをクリック - 次の設定はQflow Managerではできないのでテキストエディタで[プロジェクトディレクトリ]/layout/[プロジェクト名].parというファイルを開き、

*rowSep : 0.2 0

と修正して保存します。 - Placement: Run

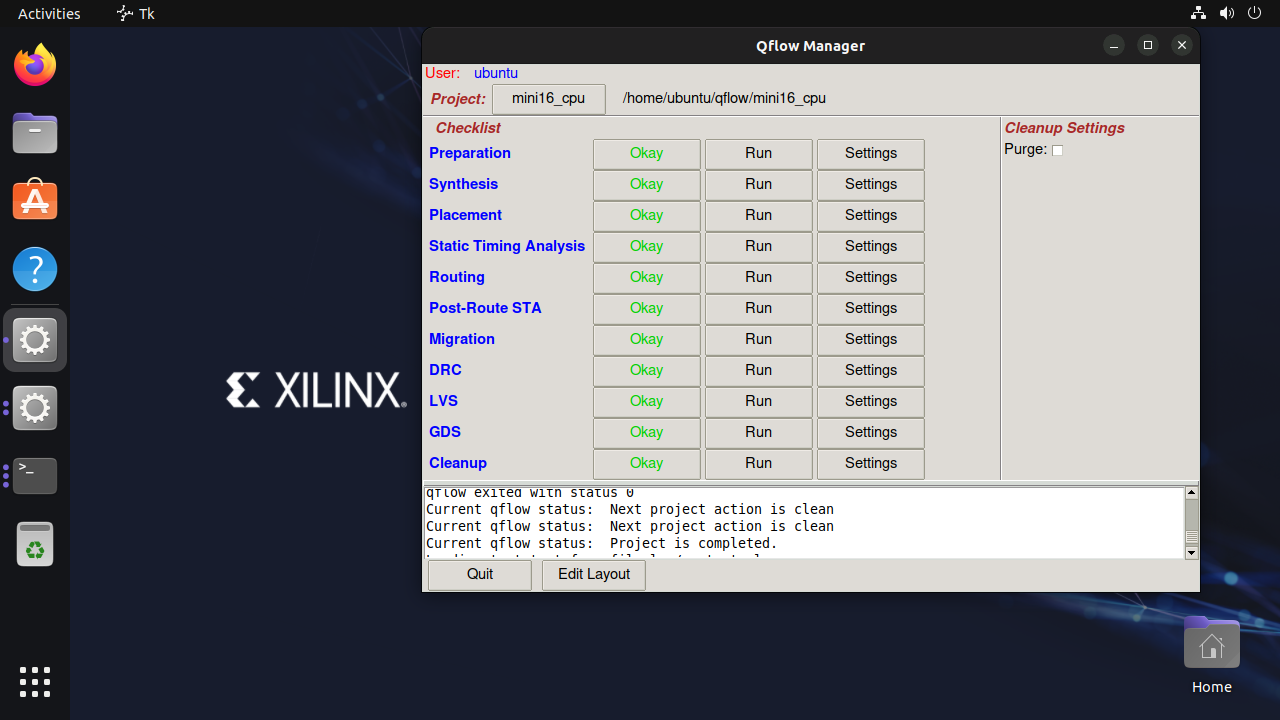

配置配線以降が順に実行されます。

全ての工程が成功すると、[プロジェクトディレクトリ]/layout/[プロジェクト名].gdsにGDSファイルが生成されます。

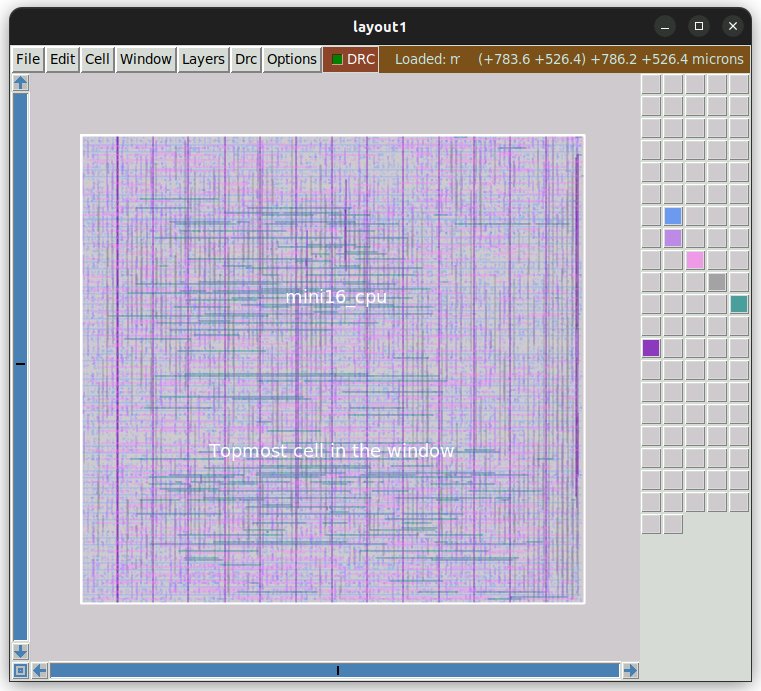

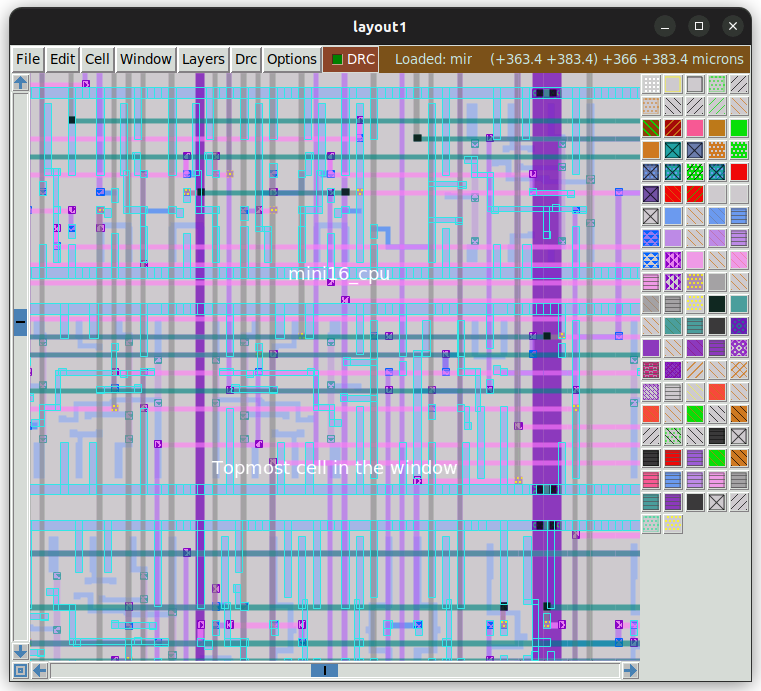

「Edit Layout」をクリックすると完成したレイアウトを確認、編集できます。

途中でFailした場合は、以下の値を変えてPlacement:Runから再実行します。

- Initial density

セル配置の密度(0.0〜1.0)。小さいほど粗くなり、配線の余裕ができますが、ダイサイズが増加し、性能は低下します。

- Aspect ratio

ダイの縦横比。1.0で正方形です。1.0以下では横長、1.0以上では縦長になります。

- rowSep

セル間の縦方向の隙間の大きさの相対値(0〜1.5)。大きいほど隙間が空いて配線の余裕ができますが、ダイサイズが増加し、性能は低下します。

使用例

Kria KV260のUbuntu22.04(今回FPGA部分は関係ありません。単なるUbuntu PCとして使用しました。)でQflowを実行し、Mini16-CPUをレイアウトしてみました。

レジスタファイル込み、メモリ含めず、ENABLE_MVIL=1, ENABLE_WA=1, ENABLE_INT=1, WIDTH_D=16, DEPTH_I=9, DEPTH_D=6の設定で180nmプロセスで生成した場合、

ダイサイズ: 0.696mm x 0.67mm (log/place.log: Core valuesより)

スタンダード・セル数: 6559 (log/synth.log: Number of cellsより)

fMax: 404MHz (log/post_sta.log: Computed maximum clock frequencyより)

となりました。

ダウンロード: qflow_mini16_cpu.tar.gz

補足情報

スタンダード・セルのレイアウトが表示されない問題

一部のファイルがパッケージに含まれていないため、DRCやGDSの設定でUse GDS view of standard cellsをオンにするとエラーが出る場合があります。また、スタンダード・セルがレイアウトに表示されません。これは、Gitリポジトリから足りないファイルをコピーすれば修正できます。

$ git clone https://github.com/RTimothyEdwards/qflow.git

$ cd qflow/tech

$ sudo cp osu018/osu018_stdcells.gds2 /usr/share/qflow/tech/osu018/

$ sudo cp osu035/osu035_stdcells.gds2 /usr/share/qflow/tech/osu035/

$ sudo cp osu050/osu05_stdcells.gds2 /usr/share/qflow/tech/osu050/

参考文献

以下は外部サイトへのリンクです。

Qflow: http://opencircuitdesign.com/qflow/

GitHub / RTimothyEdwards / qflow: https://github.com/RTimothyEdwards/qflow

MakeLSI資料: https://scrapbox.io/makelsi/