Xilinx ISE 14.7を使ってParallellaのFPGAビットストリームを生成します。その際、ユーザーロジックを追加できるよう、公式プロジェクトファイルをテンプレートにして新しいプロジェクトを作成します。

この記事では、Ubuntu 14.04上のISE 14.7を使用してビットストリームを生成します。Ubuntu 14.04へのISE 14.7のインストール方法については以下の記事を参考にしてください。

Xilinx ISE Design Suite 14.7をUbuntu 14.04にインストールする

ここではHDMIに対応した旧版SDカードイメージを使用します。Parallella公式サイトから「With Display」版(ubuntu-14.04-hdmi-z70X0-20140611.img.gz)をダウンロードしてセットアップしてください。

端末で、

cd ~

mkdir parallella_hw_projects

cd parallella_hw_projects

git clone https://github.com/parallella/parallella-hw.git

cd parallella-hw

git checkout ce97134

(ここではgit checkoutで旧バージョンを選択しています。)

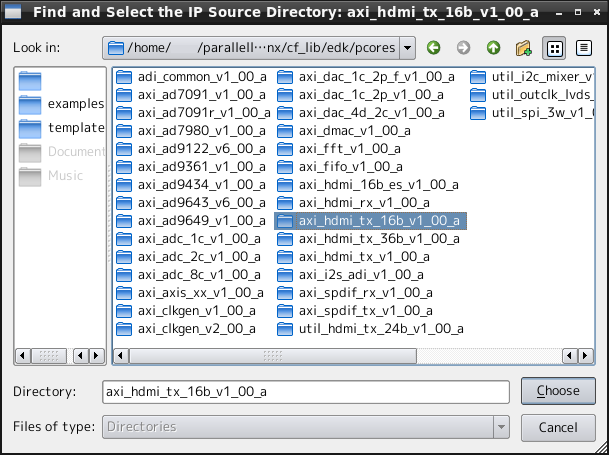

cd ~/parallella_hw_projects/parallella-hw/fpga/externals

bash get_fpgahdl_xilinx

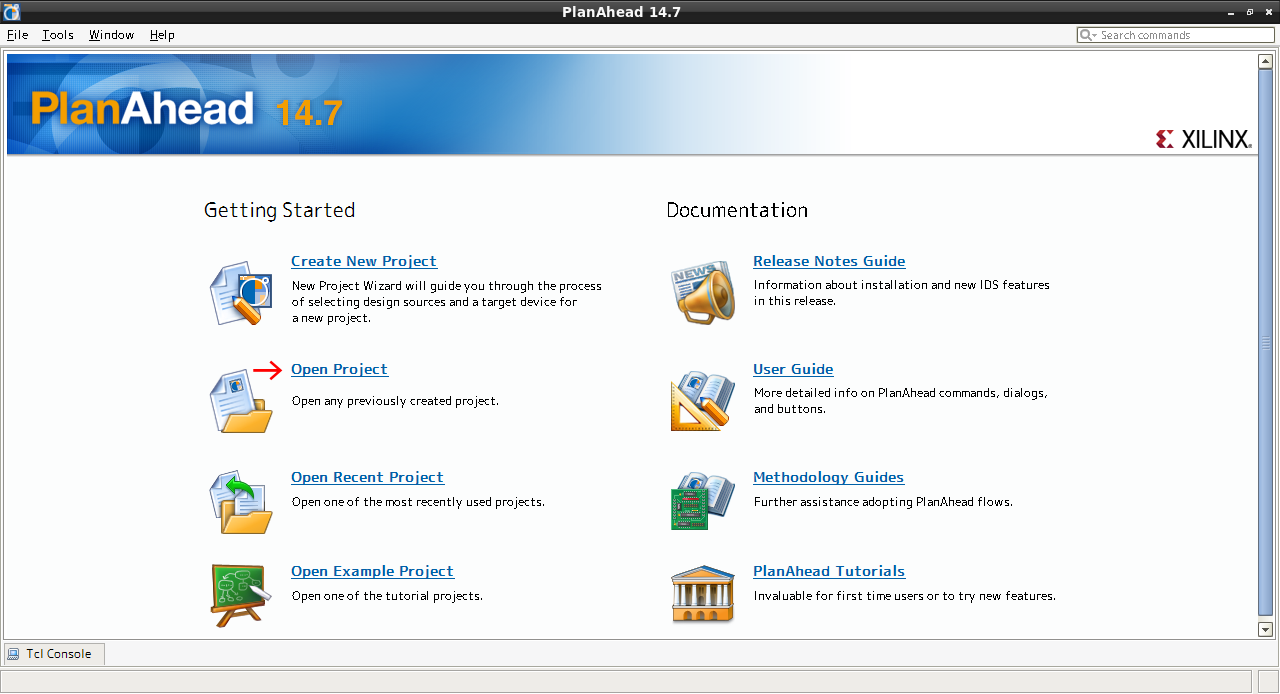

PlanAheadを起動します。

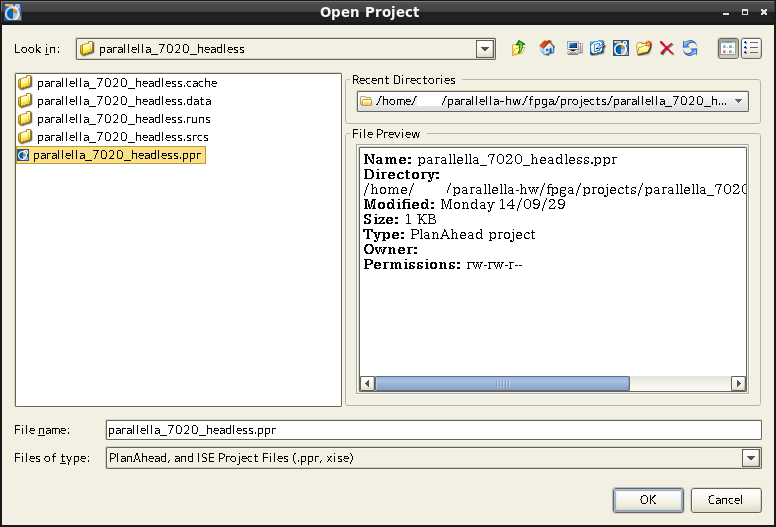

「Open Project」をクリックしてParallella HW プロジェクトを開きます。

プロジェクトファイルは、parallella_hw_projects/parallella-hw/fpga/projects/ 以下にあります。

お持ちのParallellaのバージョンに適合したファイルを開いてください。

Zynq7010版用

USB、HDMIサポートあり

parallella_7010_hdmi/parallella_7010_hdmi.ppr

ヘッドレス版(Ethernetのみサポート)

parallella_7010_headless/parallella_7010_headless.ppr

Zynq7020版用

parallella_7020_hdmi/parallella_7020_hdmi.ppr

parallella_7020_headless/parallella_7020_headless.ppr

64コア版用

parallella_64_7020_hdmi/parallella_64_7020_hdmi.ppr

parallella_64_7020_headless/parallella_64_7020_headless.ppr

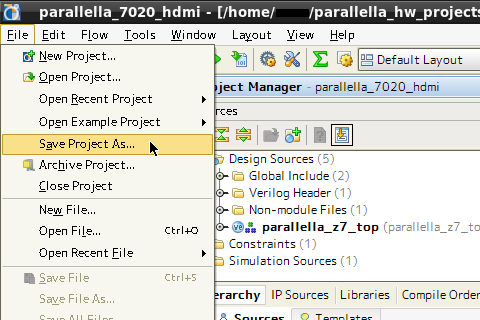

開いたプロジェクトを元にして新しいプロジェクトを作ります。

メニュー→「File」→「Save Project As...」を選択します。

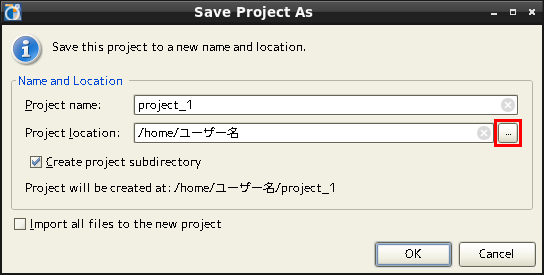

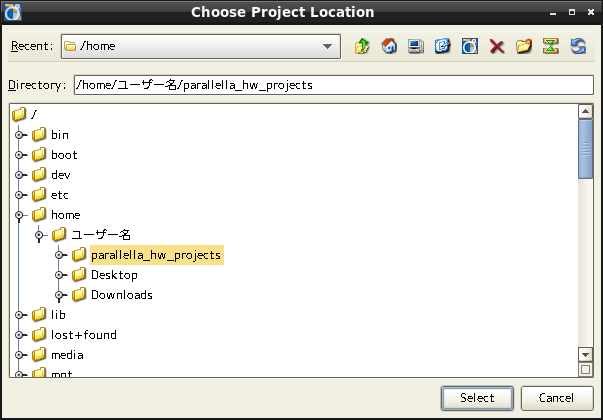

「Project Location」の行の右端の「...」をクリックします。

ホームディレクトリの下の「parallella_hw_projects」ディレクトリを選択して「Select」をクリックします。

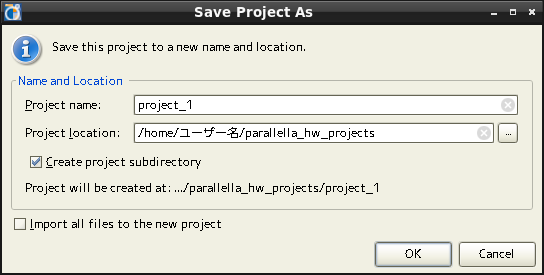

「Project name:」に新しいプロジェクト名を入力します。デフォルトでは「Project_数字」と記入されています。

ここで、「Import all files to the new project」にチェックすると、全てのファイルのコピーが新しいプロジェクト内に作成されます。チェックしなければ、元のファイルを参照する形でプロジェクトが作られます。参照する形で作っておけば、元のparallella-hwプロジェクトが更新された時には自動的にそれが使われます。逆に更新されては困る場合は全てImportしておくといいでしょう。

参照形式の場合、子プロジェクトから元のファイルを修正してしまうと、他の全ての子プロジェクトにその修正が影響してしまうことに注意が必要です。元のファイルを修正せずに、その子プロジェクト内のみで修正したい場合、以下の方法でそのファイルのみImportして使用します。

ここではこれにチェックせずに、後で必要なファイルのみImportすることにします。

「OK」をクリックします。

これで参照形式で新しいプロジェクトが作成されますが、「version.v」と「system.xmp」の2つのファイルは必ずImportしなければいけません。(これらのファイルはプロジェクト毎にほぼ確実に修正が必要なファイルのため)

「Project Manager」の「Sources」ウィンドウで「Design Sources」→「Global Include」のボタンをクリック、「version.v」を右クリックして「Copy File Into Project」を選択します。

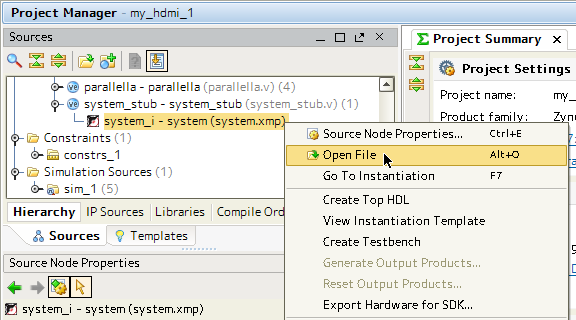

「parallella_z7_top」のボタンをクリック、「system_stub」のボタンをクリック、「system_i」を右クリックして「Copy File Into Project」を選択します。

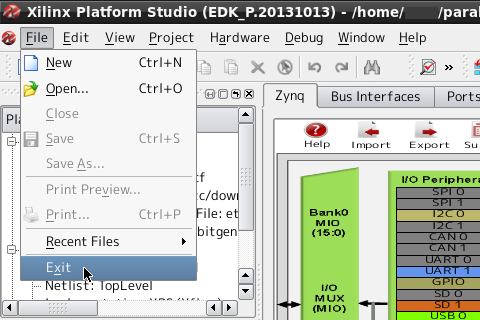

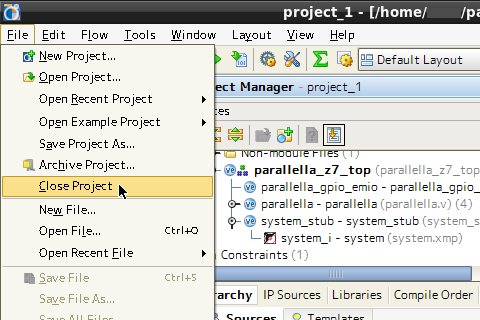

ここで一旦プロジェクトを閉じます。(エラー対策のため)

メニュー→「File」→「Close Project」をクリックします。

PlanAheadの起動画面に戻るので、改めて新しく作ったプロジェクトを開き直します。

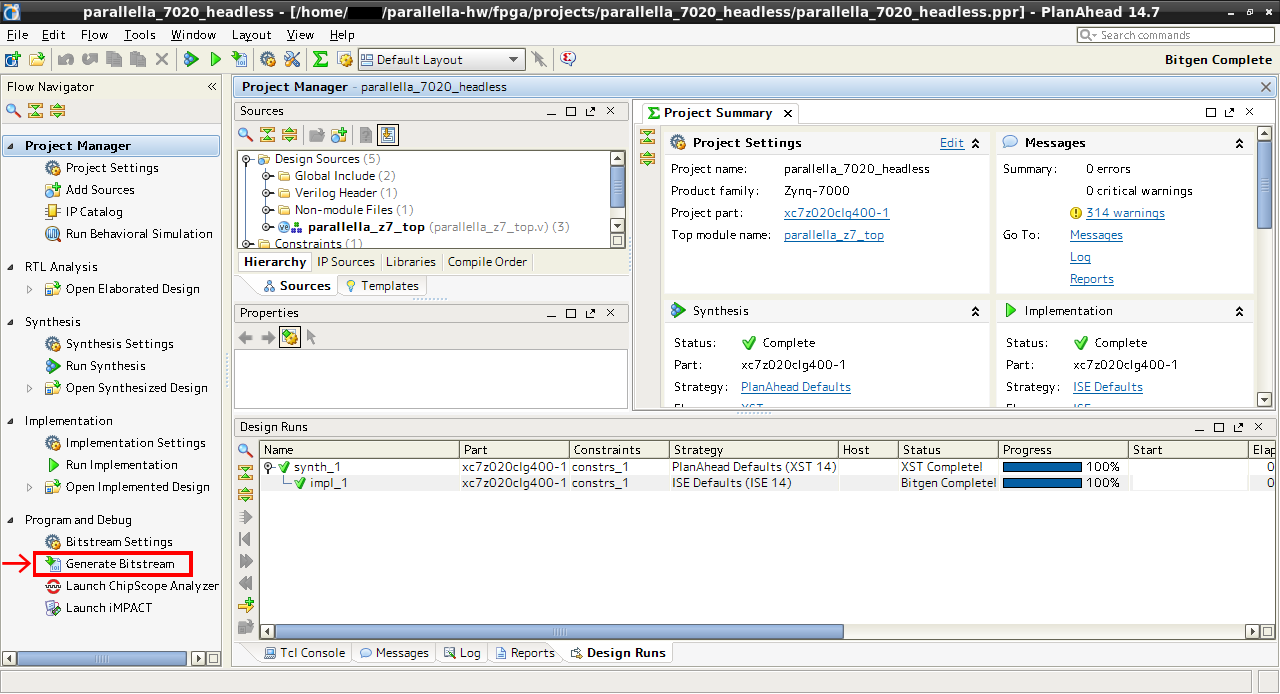

「Generate Bitstream」をクリックしてビットストリームを生成します。

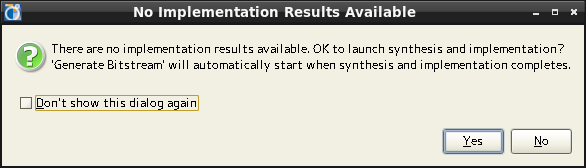

このダイアログが出た場合は「Yes」をクリックします。

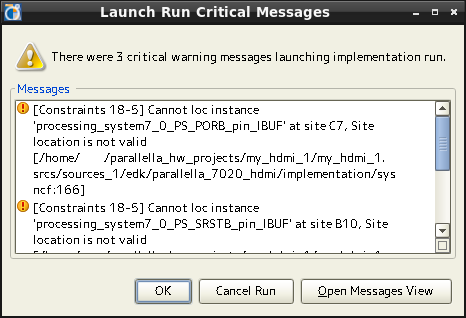

このダイアログが出た場合は「OK」をクリックします。

「OK」

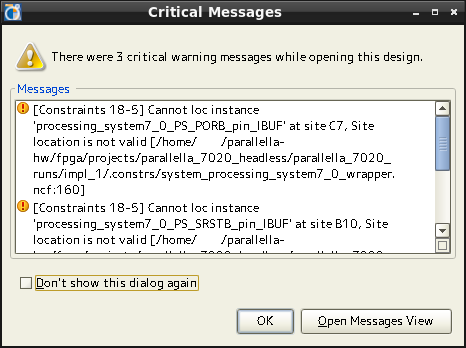

毎回このクリティカル・ワーニングが出ますがこれは無視できます。「OK」

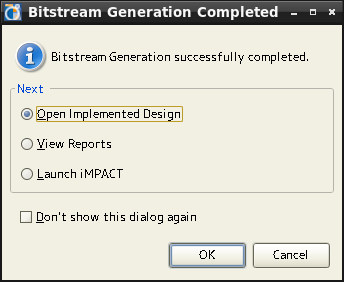

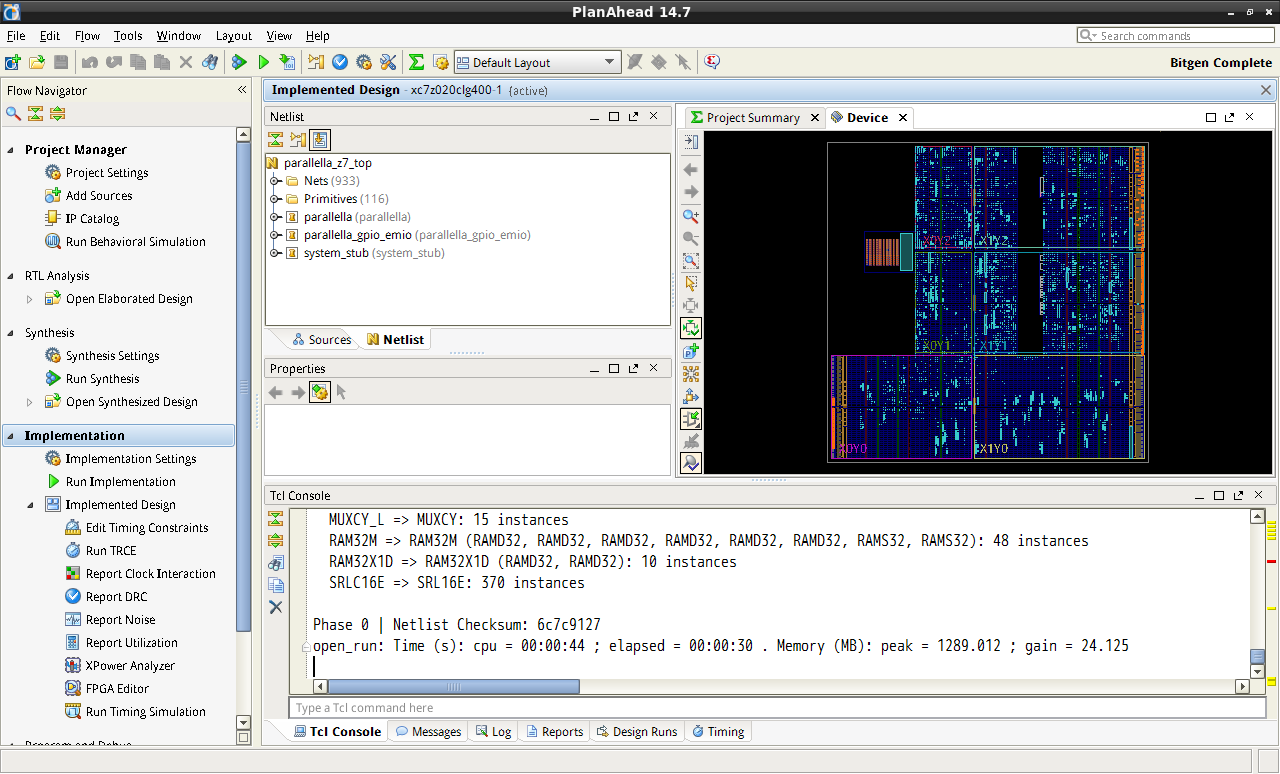

生成できました。

ビットストリームファイルは、parallella_hw_projects/プロジェクト名/プロジェクト名.runs/impl_1/ 以下に出来ています。これをRawバイナリーファイルに変換します。

cd ~/parallella_hw_projects/parallella-hw/fpga/projects/parallella_70x0_xxxx

(xの部分は各バージョンのものに置き換えてください。)

cp getbits bit2bin.bif dummy.elf ~/parallella_hw_projects/プロジェクト名/

cd ~/parallella_hw_projects/プロジェクト名/

nano bit2bin.bif

「parallella_70x0_xxxx.runs/impl_1/parallella_z7_top.bit」と書かれている行を「プロジェクト名.runs/impl_1/parallella_z7_top.bit」に修正し、保存してnanoを終了します。

mkdir bitbin

nano getbits

「mv parallella_z7_top.bit.bin ../../bitstreams/parallella_exx_xxxx_gpiose_70x0.bit.bin」の行を

「mv parallella_z7_top.bit.bin bitbin/parallella.bit.bin」に修正します。

【32bit版OSを使用している場合のみ】:「. /opt/Xilinx/14.7/ISE_DS/settings64.sh」の行を「. /opt/Xilinx/14.7/ISE_DS/settings32.sh」に修正します。

保存してnanoを終了します。

変換スクリプトを実行します。

bash getbits

parallella_hw_projects/プロジェクト名/bitbin 以下にparallella.bit.binが生成されます。このファイルをParallellaのシステムSDカードのBOOTパーティションにコピーします。ヘッドレス版の場合は、devicetree.dtbもヘッドレス版のものに入れ替えてください。

Re: FPGA Source / Project Repository (Parallella Community)

Parallella FPGA Tutorial 0: (part1) Creating a new project/repo